### SPD1188 电路设计指南

# 概述

SPD1188 是旋智推出的第三代采用系统级封装(SiP,System in a Package)的电机驱动芯片。在一颗芯片内部集成有 MCU、预驱模块和电源管理模块,单电源供电电压高达 96V,使用单芯片和简单的外围分立元件电路就能实现高性能的电机控制,成功应用于电动工具、风机和泵类等应用中。

这份文档主要介绍 SPD1188 外围电路设计指南、芯片应用中遇到的一些问题和一些实用的推荐电路。

# 目录

| 1   | SPD1188 最小系统电路设计指南              | 7  |

|-----|---------------------------------|----|

| 1.1 | 片上 MCU 与调试接口                    | 7  |

| 1.2 | 晶振电路                            | 9  |

| 1.3 | SPD1188 电源电路                    | 10 |

| 1.4 | 三相桥预驱部分电路                       |    |

|     | 1.4.1 CBOOT 电容                  | 13 |

|     | 1.4.2 VDDG 电容                   |    |

|     | 1.4.3 Charge Pump 飞跨电容 CF       |    |

|     | 1.4.4 VBAT 电容                   | 16 |

|     | 1.4.5 SPD1188 电机控制 PGA          |    |

| 1.5 | BUCK 电路元件选取方法                   |    |

| 2   | SPD1188 电机控制应用推荐电路              | 18 |

| 2.1 | 低功耗模式唤醒电路                       |    |

| 2.2 | 三相桥电源 VM 和芯片供电 VBAT 分开系统注意问题    |    |

| 2.3 | 电荷泵 VCP 输出保护                    | 20 |

| 2.4 | 下桥 Vds Monitor 功能应用限制与下桥 Vgs 走线 |    |

| 2.5 | 自举电容上电充电策略                      | 21 |

| 2.6 | 防反接电路                           | 21 |

| 2.7 | SIO CAN 通讯时钟精度要求                | 22 |

# 图片列表

| 1-1:  | SPD1188 系统功能框图                                                                                        | 7                                                              |

|-------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1-2:  | 常用芯片低电平按键复位电路                                                                                         | 9                                                              |

| 1-3:  | SPD1188 Clock tree                                                                                    | 10                                                             |

| 1-4:  | 外部无源晶振输入电路                                                                                            | 10                                                             |

| 1-5:  | SPD1188 电源架构框图                                                                                        | 11                                                             |

| 1-6:  | SPD1188 典型应用原理图                                                                                       | 12                                                             |

| 1-7:  | 单相预驱简化框图                                                                                              | 13                                                             |

| 1-8:  | 目标 MOSFET IRFR7440 的 Ciss 参数                                                                          | 14                                                             |

| 1-9:  | SPD1188 Charge Pump 工作示意简图                                                                            | 15                                                             |

| 1-10: | Motor PGA 典型应用原理图                                                                                     | 16                                                             |

|       |                                                                                                       |                                                                |

| 2-2:  | SPD1188 推荐工作条件                                                                                        | 18                                                             |

| 2-3:  | 电荷泵保护电路                                                                                               | 19                                                             |

| 2-4:  | SPD1188 防反接推荐电路                                                                                       | 22                                                             |

| 2-5:  | RCO 特性                                                                                                | 22                                                             |

|       | 1-2:<br>1-3:<br>1-4:<br>1-5:<br>1-6:<br>1-7:<br>1-8:<br>1-9:<br>1-10:<br>2-1:<br>2-2:<br>2-3:<br>2-4: | 1-1: SPD1188 系统功能框图 1-2: 常用芯片低电平按键复位电路 1-3: SPD1188 Clock tree |

# 表格列表

| 表 1-1: | 片上 MCU 调试接口引脚定义          | 8 |

|--------|--------------------------|---|

| -      | SPD1188 Boot Loader 模式选择 |   |

|        | SPD1188 供电电源管脚外部电容选型     |   |

# 版本历史

| 版本  | 日期         | 作者  | 状态  | 变更    |

|-----|------------|-----|-----|-------|

| C/0 | 2025-05-06 | 高天骥 | 已发行 | 首次发布。 |

# 术语或缩写

| 术语或缩写 | 描述 |

|-------|----|

|       |    |

|       |    |

|       |    |

|       |    |

|       |    |

# 1 SPD1188 最小系统电路设计指南

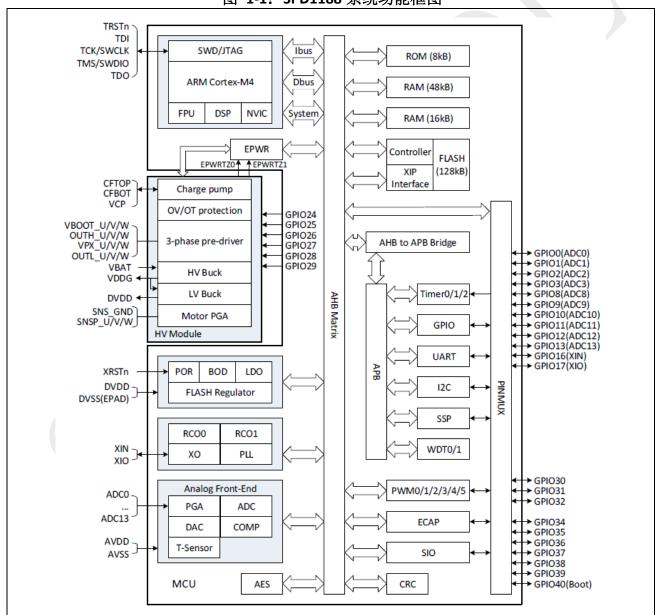

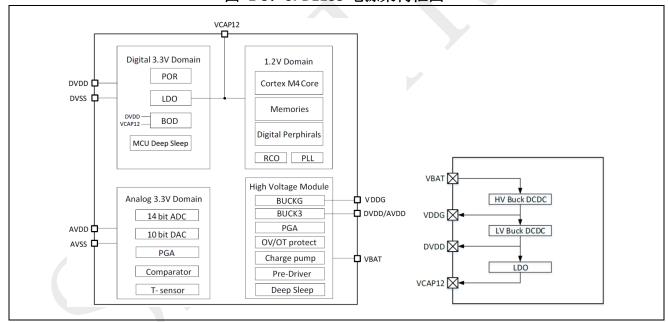

如下图 1-1, SPD1188 的最小系统电路主要包含: ①片上 MCU 与调试接口,②晶振电路,③芯片电源管理部分电路 (HV Buck, LV Buck),④三相桥预驱部分电路 (预驱,电荷泵, Motor PGA)。接下来就分上述四个部分电路分别做介绍。

SPD1188 最小系统运行条件可以总结为: 只需要为芯片提供 VBAT (8V-96V) 电源,利用片内高压 BUCK 从 VBAT 生成预驱电源 VDDG,利用片内低压 BUCK 从 VDDG 生成 MCU 供电 3.3V。片上 MCU 系统包含了一个内部 32MHz RC 振荡器,对于大多数应用可以不用外加晶振。预驱部分需要外加电荷泵电容、自举电容。

图 1-1: SPD1188 系统功能框图

# 1.1 片上 MCU 与调试接口

SPD1188 的片上 MCU 是基于 ARM Cortex-M4 CPU 内核,带 FPU 运算单元,时钟频率最高 200MHz,包含高达 128kB Flash、512 bytes OTP flash,64kB SRAM,内部集成出厂校准的 32MHz

(1%) RC 振荡器,可作为 PLL 的时钟输入。14 位 ADC,高达 8 通道 ADC 输入,三路采样保持电路,最低 140ns 的转换时间。3 个可编程运算放大器,可以做差分或者单端运放。3 个电机专用可编程增益放大器,专门用于放大处理三相桥电流电阻采样信号,输入电压可为负值。10 路高速模拟比较器,并拥有 4 个 DAC 参考源,可作为相位比较和过压保护。6 个增强型 ePWM模块,可以输出 12 路三相桥驱动信号。高达 17 个 GPIO 口。MCU 集成了增强捕获单元和 6 个定时器(3 个通用定时器,2 个看门狗定时器和一个系统滴答定时器)。一个 UART 接口,一个SPI 接口,一个 I2C 接口,一个灵活可配置的 SIO 接口。MCU 集成温度传感器及每个电源域的过欠压保护模块、上电复位和 Debug 模块。

SPD1188 MCU 部分最小系统,除了要在 MCU 电源引脚就近增加去耦合电容外,最重要的就是调试接口电路,SPD1188 调试接口为 ARM SWJ-DP 接口,这是标准的 ARM CoreSight 调试接口,包括 JTAG-DP 接口(5 个引脚)和 SW-DP 接口(2 个引脚)。SPD1188 也可以通过软件关闭调试接口。调试功能接口引脚定义见表 1-1。

| Pin  | SWJ-DP 端 | JTAG | 调试接口          | SW    | 调试接口      | 说明                                     |

|------|----------|------|---------------|-------|-----------|----------------------------------------|

| PIII | 口引脚名     | 类型   | 调试功能          | 类型    | 调试功能      | 远 切                                    |

| 56   | TMS/SWD  | 输入   | JTAG 模式<br>选择 | 输入/输出 | 串行数据输入/输出 | 多功能复用口,当 TRSTn 为高,此引脚功能为 TMS/SWD。      |

| 1    | TCK/SWCK | 输入   | JTAG 时钟       | 输入    | 串行时钟      | 多功能复用口,当 TRSTn 为高,此引脚功能为 TCK/SWCK。     |

| 54   | TDO      | 输出   | JTAG 数据<br>输出 | -     | _         | 多功能复用口,当 TRSTn 为高,此引脚功能为 TDO。          |

| 55   | TDI      | 输入   | JTAG 数据<br>输入 | -     | -         | 多功能复用口,当 TRSTn 为高,此引脚功能为 TDI。          |

| 2    | TRSTn    | 输入   | JTAG 模块<br>复位 | -     | -         | JTAG 复位引脚,低电平有效。<br>建议此引脚外置上拉为高电<br>平。 |

表 1-1: 片上 MCU 调试接口引脚定义

与程序调试相关的特别需要注意的引脚还有 BOOT 引脚、TRSTn 引脚和 XRSTn 引脚。

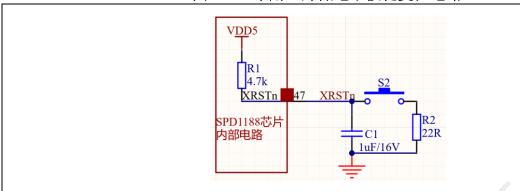

芯片 Pin 47 为 XRSTn,是芯片的全局硬件复位引脚,低电平复位整个芯片,芯片硬件复位引脚在芯片内部通过 4.7k Ω 的电阻上拉到内部 VDD5 5V 电源,确保芯片正常工作。此引脚可外加按键复位电路,常见的按键复位电路如下图 1-2 所示,按键 S2 按下,XRSTn 的电压,也就是电容 C1 两端的电压,在约 110us(5R2C1)的时间后会放电到约 0V,R2 的电阻很小,为 22 Ω,是为了限制 C1 放电时的冲击电流,XRSTn 引脚在芯片内部有除颤电路,可设置 500us~4ms的低电平除颤时间,XRSTn 低电平超过这个时间芯片才会产生复位。按键 S2 弹起,XRSTn 的电压,也就是电容 C1 两端的电压,经过 4.7ms(R1C1)会被 VDD5 充电到大于 3V,芯片退出复位状态,复位完成。也可以在此引脚增加低功耗模式唤醒电路,详见章节 2.1。如无复位电路或者唤醒电路的需求,此引脚可以悬空。详见《SPD1188\_Technical\_Reference\_Manual》章节 3.2。

图 1-2: 常用芯片低电平按键复位电路

SPD1188 的 Pin 3 是 BOOT 启动模式引脚,见表 1-2,推荐此引脚直接外置上拉电阻上拉为高电平,BOOT 程序从内部 Flash 开始运行,BOOT 引脚也可以配置为 GPIO40,且只能作为输出功能。详见《SPD1188\_Technical\_Reference\_Manual》章节 1.5。

Pin 2 是 TRSTn,为 JTAG 复位引脚,低电平有效。如果 TRSTn 为高电平,则 JTAG 和 SW 调试接口全部使能,且仅作为调试功能。为了方便调试,且在 GPIO 口富余的情况下,TRSTn 可直接外部上拉为高电平。

| 启动模式引脚选择   |             | 启动模式                                                      |  |  |  |

|------------|-------------|-----------------------------------------------------------|--|--|--|

| PIN3(BOOT) | PIN2(TRSTn) | 口列失人                                                      |  |  |  |

| 1          | x           | 正常启动模式,从 Flash 开始启动<br>当 TRSTn 为高电平时,调试接口使能               |  |  |  |

| 0          | 0           | ISP 模式 (GPIO34 被配置为 UART_TXD 功能; GPIO35 被配置为 UART_RXD 功能) |  |  |  |

| 0          | 1           | 工程测试模式。在此模式下,芯片不会正常工作,所以不<br>要选择此模式                       |  |  |  |

表 1-2: SPD1188 Boot Loader 模式选择

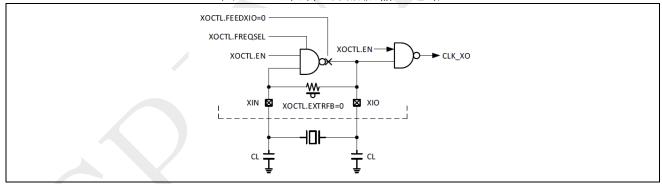

# 1.2 晶振电路

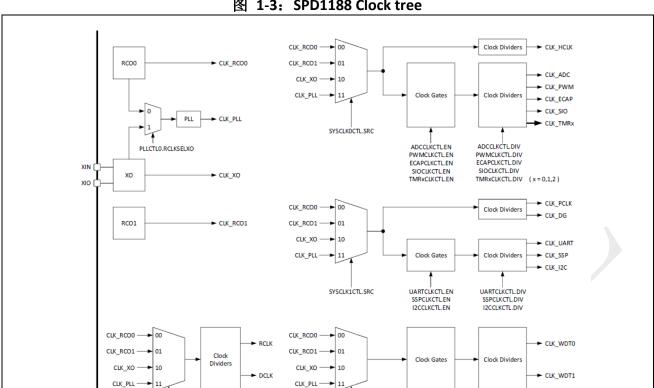

SPD1188 的时钟结构如下图 1-3 所示。

SPD1188 芯片内部有两个 RC 振荡器, RCOO 为出厂校准的 32MHz 内部 RC 时钟,可作为 PLL 的输入; RCO1 为 2.2M 内部 RC 时钟,是安全备份时钟。XO 为外部无源晶振和片内有源谐振电路组成的时钟或者外部有源晶振输入的时钟。PLL 锁相环能够提供高达 200MHz 的内部时钟。

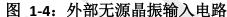

对于大多数时钟频率要求不高的场合,可直接采用芯片内部 RCOO 时钟。如果需要外加无源晶振,电路示意图如图 1-4,芯片内部集成了  $1M\Omega$  的反馈电阻,只需要外加无源晶振和两个负载电容,外加的无源晶振频率为  $1^{\sim}66MHz$ ,负载电容  $12pF^{\sim}27pF$ ,电容的选择参考晶振供应商推荐,或者通过晶振起振测试来确定。不同的外部晶振需要软件设置不同的驱动能力,详见《SPD1188 Technical Reference Manual》章节 3.6。

图 1-3: SPD1188 Clock tree

WDT1CLKCTL.SRC

WDT1CLKCTL.EN

WDT1CLKCTL.DIV

#### SPD1188 电源电路 1.3

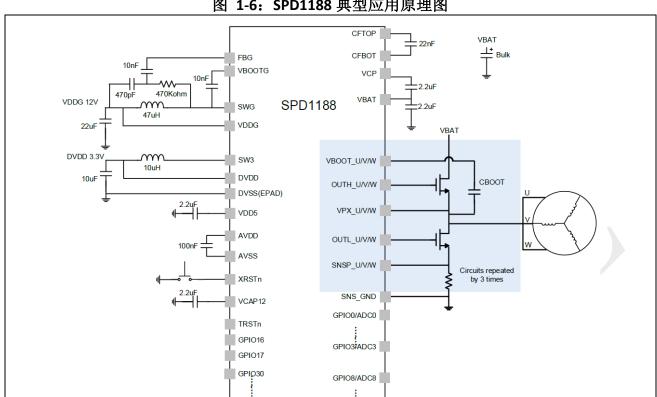

如图 1-5 所示, SPD1188 芯片运行仅需要提供 VBAT (8V~96V) 电源。

CLKDETCTL.RCLKDIV CLKDETCTL.DCLKDIV

CLKDETCTL.RCLKSRC CLKDETCTL.DCLKSRC

SPD1188 集成的电源管理模块包括高压降压式开关电源(HV Buck)和低压降压式开关电 源(LV Buck),分别提供 10V 和 3.3V 电源。当然这些电源也可以外部提供。

HV Buck 将主输入电源 VBAT 转换为 VDDG。VDDG 的典型值为 10V,输出电压 5V~18V 软 件可调,其决定了预驱输出电压的摆幅。HV Buck 采用同步整流,不需要外接 MOSFET 或者二 极管。外接补偿网络是需要的,典型应用中每个被动元件的值如下图 1-6 所示,如无特殊应用 要求,请按照推荐参数设计。当输入电压 VBAT 高于 8.15V 时, HV Buck 开始工作;低于 7.65V 时停止工作。HV Buck 典型的开关频率是 600kHz, 典型限流值为 300mA。

LV Buck 将电源 VDDG 转换为 DVDD。DVDD 的典型值为 3.3V,用于给 MCU 供电。LV Buck 采用同步整流,不需要外接 MOSFET 或者二极管,也不需要外接补偿网络。典型应用原理图如 下图 1-6 所示, 电感值采用 10uH, 输出电容值为 10uF, 最大不要超过 22uF, 如无特殊应用要

求,请按照推荐参数设计。当电压 VDDG 高于 6.5V 时,LV Buck 开始工作;低于 6.2V 时停止工作。在芯片上电过程中,LV Buck 在开始工作前会等待 HV Buck 完成软启动,通常为 1ms。LV Buck 典型的开关频率是 1.2MHz,典型限流值为 600mA。

此外,VBAT 域中的深度睡眠模式将关闭 HV 和 LV buck,以实现低至 15uA 的关闭电流。如果客户同时使用高压 buck 和低压 buck,则必须启用交叉保护功能以确保两个 buck 之间没有相互作用。详细设计请参考《SPD1188\_Technical\_Reference\_Manual》章节 25。6。

HV 和 LV Buck 均能够调整开关频率,增加频率抖动的功能,具有可调的过欠压和过流保护功能,详见《SPD1188\_Technical\_Reference\_Manual》章节 25。

SPD1188 模拟前端供电管脚 AVDD 采用上述 DVDD 相同的供电。设计电路板时,需要注意在尽量靠近 AVDD 和 AVSS 管脚的地方放置去耦电容。建议将 DVDD 电源通过一个高频磁珠供给 AVDD。AVSS 和模拟测量调理电路以及滤波电路的地统称为 AGND,并在 PCB 上和数字地 DGND 一点接地。

SPD1188 内部有集成 Power-on-reset (POR)模块,可以保证芯片的各个电源上电时序符合要求,使芯片更易使用。DVDD 和 DVSS(EPAD)之间、VCAP12 和 GND(EPAD)之间、AVDD 和 AVSS 之间、VBAT 和 GND(EPAD)之间、VDDG 和 GND(EPAD)之间、VDD5 和 GND(EPAD)之间均需要在靠近芯片引脚的位置放置高频去耦合电容,电容容值选型见表 1-3。

图 1-5: SPD1188 电源架构框图

图 1-6: SPD1188 典型应用原理图

表 1-3: SPD1188 供电电源管脚外部电容选型

GPIO40

GPIO13/ADC13

| Pin | 信号名    | 类型 | 描述                                                                                                                                                                                                               |

|-----|--------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | VCAP12 | 电源 | 内部 1.2V, 在 VCAP12 和 GND 管脚之间就近放置 0.1uF 的高频去耦合电容。                                                                                                                                                                 |

| 7   | AVDD   | 电源 | 模拟电源输入,在 AVDD 和 AVSS 管脚之间就近放置 0.1uF 的高频 去耦合电容。                                                                                                                                                                   |

| 8   | AVSS   | 电源 | 模拟地。                                                                                                                                                                                                             |

| 15  | DVDD   | 电源 | LV Buck 输出电压,3.3V 反馈点,数字电源输入,因为低压 Buck 已经在靠近电感处放置了 10uF 的输出电容,所以在芯片 DVDD 和 GND 管脚之间只需要就近放置 0.1uF 的高频去耦合电容,如果 Buck 输出距离电源输入引脚较远,可在管脚就近增加 2.2uF 的电容。低压 Buck 输出电容推荐值为 10uF,也就是 3.3V 输出网络上的总电容之和要等于 10uF,最大不超过 22uF。 |

| 16  | VCAP12 | 电源 | 内部 1.2V, 在 VCAP12 和 GND 管脚之间就近放置 2.2uF 和 0.1uF 的高频去耦合电容。芯片内部 1.2V 电源已经连接在一起了,在 PCB 板上,不需要将芯片的两个 VCAP12 引脚连接在一起。                                                                                                  |

| 29  | VDDG   | 电源 | HV Buck 输出电压,VDDG 反馈点,下桥驱动和电荷泵供电电源,5V~18V 可编程输出电压,HV Buck 输出电容推荐值为 22uF,Buck 输出电容需要靠近电感放置,在芯片 VDDG 和 GND 管脚之间只需要就近放置 0.1uF 的高频去耦合电容。                                                                             |

| 31 | VBAT | 电源 | 芯片供电电源输入,在 VBAT 和 GND 管脚之间就近放置 2.2uF 和 0.1uF 的高频去耦合电容。VBAT 也是三相桥的输入电压,为了满足电机控制的需求需要增加大容量的电解电容,具体的选择原则见后续 1.4 节分析。 |

|----|------|----|-------------------------------------------------------------------------------------------------------------------|

| 46 | VDD5 | 电源 | 芯片内部 5V 电源,在 VDD5 和 GND 管脚之间就近放置 2.2uF 和 0.1uF 的高频去耦合电容。                                                          |

| 48 | DVDD | 电源 | 数字电源输入,在 DVDD 和 GND 管脚之间就近放置 0.1uF 的高频去耦合电容。                                                                      |

|    | EPAD |    | 芯片 GND 平面,需要根据芯片推荐的焊盘封装,将 EPAD 可靠的连接到 GND 地平面。使得芯片所有的电源和滤波都有低阻抗的地回路,且增加芯片散热。                                      |

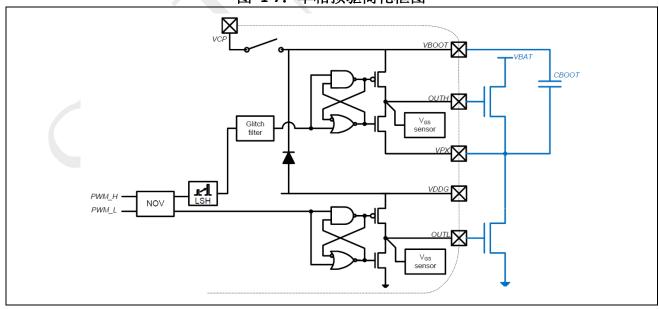

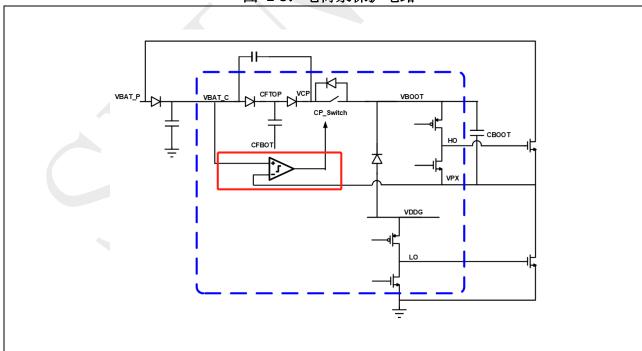

### 1.4 三相桥预驱部分电路

如图 1-6, SPD1188 典型应用电路图,预驱部分外围电路主要包括:①上桥驱动自举电容 CBOOT;②电荷泵电路:包含 CFTOP 和 CFBOT 之间的飞跨电容 CF、电荷泵输出 VCP 对 VBAT 的 稳压电容 CCP,电荷泵输出电压 VCP 主要的作用是:在上桥导通时给自举电容 CBOOT 补充电荷,从而达到上桥 100%占空比导通的功能;③电机控制专用 Motor PGA。

下面主要分析以上三部分电路的设计原则。

注:以下数值带有上标\*表示该数值为芯片设计值,生产时候不做为卡测标准。

#### 1.4.1 CBOOT 电容

SPD1188 提供三相下管和上管驱动输出,上桥采用自举电容驱动,芯片内部集成了自举二极管, U/V/W 每相驱动原理如图 1-7 所示。

图 1-7: 单相预驱简化框图

自举电容 CBOOT 的选择推荐遵循以下两个方法:

1. CBOOT 电容中的电荷用于给三个半桥电路上桥驱动的供电,当上桥打开时,CBOOT 中的电荷会向 MOSFET 的 GS 端充电,为了防止因为 CBOOT 的电容不足,造成最后 MOSFET 的 GS 驱动电压波动,需要选取一个较大的 CBOOT 值,一般根据经验**公式 1.1** 计算 CBOOT,

举例根据图 1-8 中 MOSFET 的参数,推荐的 CBOOT 为大于 50nF,一般 CBOOT 选择 100nF: CBOOT > 10\* Ciss (MOSFET 输入电容)  $\approx 50nF$  公式 1.1

#### 图 1-8: 目标 MOSFET IRFR7440 的 Ciss 参数

| ٦                |                              |   | ٠.   |   |    |

|------------------|------------------------------|---|------|---|----|

| Ciss             | Input Capacitance            | _ | 4610 | _ | pF |

| Coss             | Output Capacitance           | _ | 690  | _ |    |

| C <sub>rss</sub> | Reverse Transfer Capacitance | _ | 460  |   |    |

|                  |                              | 1 |      |   | l  |

2. 当上桥已经打开后,上桥驱动有一定的漏电,这个漏电流约为 800uA\*, 这部分漏电会 汲取 CBOOT 上的电荷。这个漏电流并不大,但如果 CBOOT 长时间没有得到补充,还是会 造成 CBOOT 上的电压明显下降,进而影响到上桥 Mos 的开通。

SPD1188 芯片中集成了 Charge Pump,在上桥 MOSFET 开通再经过过消隐时间与滤波时间之后,该功能可以持续的为 CBOOT 补充电荷。Charge Pump 默认打开(推荐),但用户也可以根据自身需求手动关闭。

1. Charge Pump 功能使能时: 此时 CBOOT 上的电荷需要保证在消隐时间 t<sub>blank</sub> 与滤波时间 t<sub>filter</sub> 之内,CBOOT 上的电压跌落小于 Δ V,t<sub>blank</sub> 和 t<sub>filter</sub> 均可以通过软件设置,最大值为 3.2us, Δ V 可以选取为 1V,则此时 CBOOT 需要大于:

CBOOT >

$$(800\text{uA}*(t_{blank} + t_{filter})/\Delta V) \approx 480\text{pF}$$

公式 1.2

由此可见,一般情况下,当 Charge Pump 可以正常作用的情况下,对于 CBOOT,因为上桥漏电产生的压降很小,应用中可以不用过多关注。

2. Charge Pump 功能禁用时:此时在上桥开通后,CBOOT 的电容无法得到补充,会因为漏电电流,随时间逐渐降低。此时若希望在  $\Delta$ t 时间内,CBOOT 上的电压跌落小于  $\Delta$ V,  $\Delta$ V 可以选取为  $\Delta$ V,  $\Delta$ t 选取为  $\Delta$ Sms,则推荐的 CBOOT 需要大于:

CBOOT >

$$(800uA * \Delta t) / \Delta V \approx 5uF$$

公式 1.3

综上,可以根据是否需要上桥长时间导通,然后分别根据**公式 1.1** 或者**公式 1.3** 来选取 CBOOT 的大小。

上电后,自举电容器为低电压,未充电。为了避免误操作,必须在上管开启前对自举电容器充电。用户必须首先施加下管的 PWM 脉冲,通过图 1-7 所示的自举二极管对 VPX 节点放电并对自举电容器充电。注意,此信号必须在 VCP 就绪状态(通常在启用预驱系统后的 2ms内)输出后才可以应用。对于 100nF 的自举电容器,下桥导通脉冲长度必须至少为 6us,并且对于较大的自举电容器值,脉冲长度必须与该数字成比例。

## 1.4.2 VDDG 电容

VDDG 上的电能用于:

1. H 桥下桥驱动,此时 VDDG 的电能用于充满 3 路下桥 MOSFET 的 Cgs 和 Cgd,或者等效为 Ciss,考虑到 IRFR7740 的例子,我们可以计算为:

- 2. 当上桥 CBOOT 为零或较低时,下桥打开后,电能将从 VDDG 电容搬运到 CBOOT 电容上,这部分一般会用较长的一段时间完成,所以对 VDDG 的容量要求并不高;

- 3. 当上桥持续开通时候,Charge Pump 持续给上桥 CBOOT 补充电能,其中 Charge Pump 一半的电能来自于 VDDG 电容,这部分基本等于上桥驱动漏电流的一半,在之前的**公式 1.2**

中,可以看出这部分数量较小,可以不予考虑。

VDDG 的电容的大小会影响 VDDG 电压本身的稳定性,一般情况下,电容越大,稳定性越好,考虑公式 1.4 和一般元件的选取方便,推荐 CVDDG = 22uF。

#### 1.4.3 Charge Pump 飞跨电容 CF

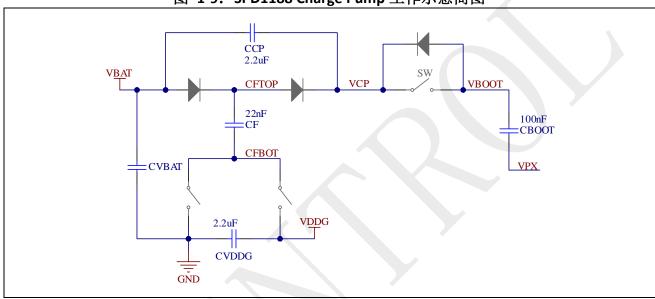

SPD1188 的 Charge Pump 结构如下图 1-9 所示,和常规的 Charge Pump 稍微有点差别,在上桥导通之后 SW 开关经过固定的延时后打开,VCP 直接给 CBOOT 电容充电,维持上桥 100% 占空比导通。每相都有单独的电荷泵连接开关。

图 1-9: SPD1188 Charge Pump 工作示意简图

如果上桥 MOSFET 打开,Charge Pump 开始工作,VDDG 电容、CF 电容在 Charge Pump 中会被交替使用。

Charge Pump 的工作分为两个阶段(Charge Pump 工作频率约为 625k Hz\*):

- a) CF 电容下端 CFBOT 连接到 GND,此时 VBAT 如果高于 CFTOP,则 VBAT 向 CF 电容充电:

- b) CF 电容下端 CFBOT 连接到 VDDG, 此时 CFTOP 电压如果高过 VBOOT 电压,则 CF 电容向 CBOOT 电容充电。

所以设计的时候,需要注意以下两个方法:

1. CF 电容在极端情况下需要完全供给 3 个上桥 CBOOT 电容的电量,所以在既定的 625k Hz\*的动作频率下,CF 电容至少要保证 CBOOT 电压的稳定。因为 Charge Pump 本身在高速开关,所以对于 CBOOT 看到的等效 CF 电容也会被几乎按照开关频率放大,即是 CF<sub>effetive</sub> ≈ 625k \* CF,设计时候保证 CF<sub>effective</sub> 大于 100 倍 3\*CBOOT 就可以。因为 CF<sub>effective</sub> 相比于 CF本身有很大的放大系数,所以这里推荐用 22nF 即可满足几乎所有应用需求。

2. CF 电容在向 CBOOT 电容充电时候,会从 VDDG 中抽取一部分电能,为了避免 VDDG 上的电压出现突变,那么会要求:

$$C_{VDDG} \gg 10 * CF$$

公式 1.6

但一般情况下,在上一节中,CVDDG 一般都会选取一个较大的值,这个限制往往不会考虑到。

另外也不希望 CF 电容引起 VCP 电容 CCP 的突变,也希望: CCP >>10 x CF,一般情况下,建议 CCP = 2.2uF,或者至少大于 1uF。

#### 1.4.4 VBAT 电容

根据 VBAT 是否直接连接到主电源 VM 上,分成下面两种情况:

1. VBAT 直接连接到 VM 上,则 VBAT 的大小应该根据掉电后需要至少工作的时长  $\Delta$  T 和最大功率  $P_{Max}$  来算。

$$\frac{1}{2} * C_{VBAT} * U_{Norm}^{2} - \frac{1}{2} * C_{VBAT} * U_{shutdown}^{2} \ge P_{Max} * \Delta T$$

$$C_{VBAT} \ge 2 * P_{Max} * \Delta T / (U_{Norm}^{2} - U_{shutdown}^{2})$$

公式 1.8

其中 UNorm 是正常工作电压, Ushutdown 是掉电保护电压。

2. VBAT 与 VM 通过二极管相连,则此时 VBAT 的负载为 SPD1188 以预驱电路,可以一般的按照 SPD1188 消耗典型功率小于 1.2W\*来计算:

$$\frac{1}{2} * C_{VBAT} * U_{Norm}^{2} - \frac{1}{2} * C_{VBAT} * U_{shutdown}^{2} \ge 1.2W * \Delta T$$

$$C_{VBAT} \ge 1.2W * \Delta T / (U_{Norm}^{2} - U_{shutdown}^{2})$$

公式 1.10

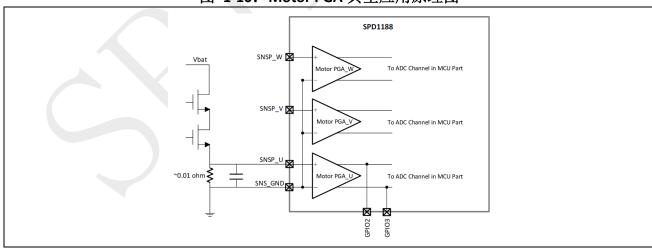

#### 1.4.5 SPD1188 电机控制 PGA

SPD1188 MCU 单元除了内置 3 个灵活的可编程增益差分放大器外,内部还集成了 3 个电机电流采样专用差分 PGA。这些 Motor PGA 的共模电压可以接近于 GND,因而适合于直接对电机电流进行采样,而不需要用外部电阻电平移位器,模拟输入端电压范围可达 -2.1V~VDDA/2,这大大简化了三相桥电流采样外围电路的布局。Motor PGA 的典型应用原理图如下图 1-10 所示。可编程的增益通过选择不同的反馈电阻 R<sub>f</sub> 来实现。由于设计的原因,当使用 Motor PGA 时,GPIO2 和 GPIO3 引脚必须浮空。

图 1-10: Motor PGA 典型应用原理图

# 1.5 BUCK 电路元件选取方法

SPD1188 内部高压模块电源管理部分集成了两个 BUCK 控制器,一个高压 HV BUCK 和一个低压 LV BUCK。

HV BUCK 从主电源 VBAT 上降压生成 VDDG 电源(默认输出 12V,可编程输出 5V~18V),此 BUCK 使用同步整流,BUCK 开关均集成在芯片内部,只需要在芯片外围添加 BUCK 电感、输

出电容和板载补偿网络,每个无源元件取值如图 1-6 所示,BUCK 电感建议选择 47uH,饱和电流大于 300mA,因为 HV BUCK 的输出限流值为 300mA,要保证在输出短路的情况下电感也不能饱和。BUCK 输出电容建议选择 22uF 陶瓷电容。HV BUCK 默认开关频率为 1.2MHz,开关频率可程序调整,且具有可编程的频率抖动功能。

LV BUCK 从 VDDG 上生成 DVDD 3.3V MCU 供电电源,LV BUCK 使用同步整流,BUCK 开关集成在芯片内部,只需要在芯片外部添加 BUCK 电感和输出电容,不需要补偿网络。LV BUCK 电感选择 10uH,饱和电流大于 500mA,因为 LV BUCK 的输出限流值为 500mA,要保证在输出短路的情况下电感也不能饱和。输出电容建议选择 10uF 陶瓷电容。LV BUCK 默认开关频率为1.2MHz,开关频率可程序调整,且具有可编程的频率抖动功能。

Buck 可以工作在 PFM 模式或者 PWM 模式,且用户可以强制锁定在 PWM 模式。当它工作在这两种不同的模式下,其电压纹波可以通过如下公式计算:

PWM 模式纹波:

$$V_{Ripple\_PWM} = \frac{{T_{sw}}^2 \cdot Vout \cdot (Vin - Vout)}{8 \cdot L \cdot C_{out} \cdot Vin}$$

$$V_{Ripple\_PFM} = \frac{{T_{sw}}^2 \cdot Vout \cdot (Vin - Vout)}{2 \cdot L \cdot C_{out} \cdot Vin}$$

可以看出在 PWM 模式下,其纹波较小。在纹波敏感和调节值敏感的应用中,建议将 DCDC 配置为强制 PWM 模式,调节器将允许电流从 SW\_DCDC 流到地面,这会降低效率,但会提供更好的输出纹波性能。在 PFM 模式下,电感电流被阻止从电感流回 GND,从而以更高的输出电压纹波为代价提高了效率。

BUCK 电感和输出电容越大,则 BUCK 的输出纹波越小,但是 BUCK 的动态响应会变慢,如果 VDDG 电源仅供芯片使用,建议按照芯片推荐选型,因为这是经过优化和测试后的值。如果有特殊应用,请重新计算和测试 BUCK 纹波、开关机和动态响应等 BUCK 特性。

# 2 SPD1188 电机控制应用推荐电路

### 2.1 低功耗模式唤醒电路

SPD1188 的 XRSTn 引脚在芯片内部通过一个 4.7kohm\*的电阻上拉到 VDD5,当芯片处于休眠状态时,如果 XRSTn 引脚,没有做特别处理,它的电平为 5V,如果在这个引脚上施加一个有效的低电平,芯片会从休眠状态跳到 Reset 状态。

应用这一特性,设计了如图 2-1 的唤醒电路: 其中 ON/OFF 接入唤醒信号,这个信号可以是 PWM 输入,或者 LIN/RS485 的 RX 输入,ON/OFF IN 是 SPD1188 的某个引脚,把 ON/OFF 信号引入 MCU 实现通信或控制。注意 D8,D9,D10 均需要选择肖特基二极管,要确保如图 2-1 小电流工作(30mA 左右)情况下二极管的压降尽量要小于 0.4V。

+3.3V DS16W Tub/10V±10% DS16W DS16W

图 2-1: 实用唤醒电路示例

此电路的工作状态分为一下三种:

- 初始状态:系统正常工作,此时 3.3V 存在, XRSTn 被 D10 上拉到 3.3V,此时 ON/OFF 即 使是 0V,因为电阻 R51=100ohm 的存在, XRSTn 的电平也不会受影响,系统可以保持正常工作。

- 休眠状态:系统收到休眠指令,进入 Sleep 模式,3.3V BUCK 电源关闭,XRSTn 在芯片内部被 VDD5 上拉至 5V;只要 ON/OFF 没有有效低电平,则系统保持在休眠模式,休眠电流最低可以到 15uA。

- Reset 状态(被唤醒状态):系统之前在休眠状态,无 3.3V 电源,ON/OFF 控制点接收到低电平,R51 相比 VDD5 对 XRSTn 的上拉电阻 4.7kohm 小很多,此时 VXRSTn  $\approx$  (5-0.4) /4.7k\*100+0.4  $\approx$  0.5V,可以产生一个有效的复位电平(SPD1188 的最高复位电平见下表)。系统进入复位状态,然后 3.3V 电源重新上电生成,XRSTn 被拉高至 2.9V(3.3V-0.4V),系统进入正常工作状态。

| Symbol          | Parameter                | Conditions              | Min                  | Nom | Max                  | Unit |

|-----------------|--------------------------|-------------------------|----------------------|-----|----------------------|------|

| $V_{\text{DD}}$ | Supply voltage           | -                       | 2.97                 | 3.3 | 3.63                 | V    |

| Vss             | Supply ground            | -                       | -                    | 0   | -                    | ٧    |

| $V_{DDA}$       | Analog supply voltage    | -                       | 2.97                 | 3.3 | 3.63                 | ٧    |

| Vssa            | Analog ground            | -                       | -                    | 0   | -                    | V    |

| VIH             | High-level input voltage | V <sub>DD</sub> = 3.3 V | 2.0                  | -   | V <sub>DD</sub> +0.3 | V    |

| VIL             | Low-level input voltage  | V <sub>DD</sub> = 3.3 V | V <sub>SS</sub> -0.3 | -   | 0.8                  | V    |

图 2-2: SPD1188 推荐工作条件

### 2.2 三相桥电源 VM 和芯片供电 VBAT 分开系统注意问题

如图 1-6, SPC1188 片上系统(MCU,电源管理,预驱)的电源都是 VBAT, 这个 VBAT 也是三相桥供电电源 VM(上桥 MOSFET 的 D 极电压),即 VBAT=VM。预驱的电荷泵电路的电源是 VBAT, 如章节 1.4.3 分析,预驱的输出电压 VCP=VBAT+VDDG-2\*0.7V,使能电荷泵电路之后,在上桥打开之后,芯片内部电荷泵开关在经过一个软件可配置的消隐时间之后会将 VCP 电压

加到 Vboot,也就是加到上桥 MOSFET 的 G 极,电荷泵的存在这是为了保证上桥 MOSFET 的 100%占空比导通,在上桥开通之后,由电荷泵 VCP 提供上桥 Vgs 维持导通需要的电流,那么上桥 MOSFET 的 GS 电压等于 VCP-VM(上桥开通之后,上桥的 S 极电压就是三相桥供电 VM),也就是 Vgs 上桥= VBAT+VDDG-2\*0.7-VM=VDDG-1.4V。这也是我们芯片推荐的三相桥系统连接方式。

但是有些应用需要将三相桥供电 VM 和 SPD1188 的 VBAT 供电分开,实现方式包括在给三相桥供电处增加总开关或者机械开关;三相桥供电增加一个防反接二极管供给芯片 VBAT;芯片供电和三相桥供电完全采用两个供电电源等。这样做带来的问题就是预驱的供电和三相桥是分开的两个电源,在使能电荷泵时,上桥开通时 Vgs 上桥= VBAT+VDDG-1.4-VM。由于 VBAT 和 VM 是两个电压,那么就必需要格外注意上桥 Vgs 电压可能会存在过压的问题。原因可能是三相桥供电电压 VM 可能由于大负载发生较大幅度跌落;或者三相桥供电 VM 在机械开关断开后,系统持续工作,VM 持续减小等因素,导致上桥 Vgs 发生过压。解决方案有以下几种:

- a) 不使能电荷泵,上桥 MOSFET 仅采用自举电容驱动的方式,上桥不能 100%占空比导通。如章节 1.4.1 分析,上桥在开通之后,上桥 Vgs 大约会有 800uA 的电流消耗,这时候就需要计算好自举电容 CBOOT 的大小、最大的上桥导通占空比和最小的下桥导通占空比,并在软硬件设计时加以限制。

- b) 使能电荷泵。使用 Vds monitor 功能提前关闭电荷泵输出 VCP 的开关。

在 SPD1188 有逻辑电路,可以在触发 VDS monitor\*\*(VDS monitor 是通过在上管开通时候,监控 DS 两端电压来判断是否出现短路或直通现象的一种保护机制。)的条件下关闭 CP\_Switch,此逻辑为 power 芯片内部组合逻辑,所以不影响其他功能。如图 2-3 所示,芯片内部硬件逻辑电路实现上桥 Vds 监控功能,也就是在上桥打开后来判断芯片 VBAT 减去三相桥供电电压 VM 之间的差值。

图 2-3: 电荷泵保护电路

启用这一功能,需要将 PDRVCTL.CPPROTEN 这个 bit 置高即可。这一位寄存器 CPPROTEN,1: 出现 VDS Monitor 告警时,关闭电荷泵,0: 无动作。

使用这种方式的时候,需要设置:①设置较小的 t\_blank+t\_filter;②软件中保证上桥关闭时间不会小于上述时间,也就是上桥在这种情况下不能 100%占空比导通。

优点: 当 VM 比 VBAT 较低时候,可以让电荷泵不要接入,从而 Vboot 电压和 vpx 之间的压差不会超过 Vddg 电压。在这种情况下,实际就可以省略之前提到的在 HO 和 VPX 之间增加的齐纳二极管。

缺点:①因为 Vds monitor 的电压触发阈值最大 2.4V(一般建议此时设定为 2.4V 阈值),则当 VM 比 VBAT 低过大约 2.4V 之后,电荷泵就无法介入,如果 Cboot 电容上掉电较快,则可能出现上桥无法正常开通。②如果为了让在出现压差较大的情况下,电荷泵尽快关闭,则 Vds Monitor 的 Blanking time 和 Filter time 要选的比较小,此时可能存在当 VBAT - VM 接近 2.4V 阈值时候就可能会出现误触发 Vds monitor 保护,从而提前关闭电荷泵的情况。

c) (3) 使能电荷泵的情况下,为了放置上桥 MOSFET 的 Vgs 过压可以在上桥的 Vgs 增加 TVS 管或者稳压二极管,进行 Vgs 电压的钳位保护。

另外,需要注意在三相桥供电 VM 和芯片供电 VBAT 分开的系统中,也要注意考虑三相桥供电 VM 突然比芯片供电 VBAT 高很多的情况,这时在上桥开通的时候 Vboot 的电压=VPX+CBOOT 电压=VM+CBOOT 电压将会大于 VCP 电压,根据图 1-9,Charge Pump 内部电路图,这时候 VBOOT 将会对 VCP 充电,有可能会导致 VCP 过压,这时候就需要在 VCP 和 VBAT之间增加稳压二极管来进行钳位保护。同时这种反向充电有可能会造成电荷泵内部开关 SW 反并联寄生二极管过流损坏,这时就需要在 VBOOT 增加限流电阻。

#### 2.3 电荷泵 VCP 输出保护

在 SPD1188 的设计中,当 VCP-VBAT > 6.8V\*之后,VCP 才会被允许连通到 Cboot。如果 VCP-VBAT < 6.1V\*,在默认配置下,则会造成 SPD1188 认为电荷泵未准备好,默认情况下会关闭上桥输出。电荷泵的工作原理如图 1-7 所示,一个开关将电荷泵的输出 VCP 连接到 VBOOT。每相都有自己的电荷泵连接开关。典型的开关频率为 625kHz。在上管侧接通后,开关在固定的时间 延迟后打开。 延迟时间应该足够大,以确保开关噪声消失, 延迟时间由寄存器 PDRVOCCTL.DGWIN 和 PDRVOCCTL.BLANKWIN 控制。实际的延迟时间是消隐时间与滤波时间之和(t blank+t filter)。

但在上桥关闭后,这个延迟逻辑同样会被触发,如果条件:上桥关闭 HO\_OFF 的时间小于 t blank + t filter,则会造成这一相上桥在打开的瞬间,这相的电荷泵就会被接入电路。

在这接入的瞬间,如果 Vpx 还较低,则 Vboot=Vpx+VDDG 也较低,VCP 的电压会被 Vboot 拉低,具体数值取决于①VCP、Cboot 电容大小②Vboot 和 VCP 压差;

如果 VCP 电压被拉到较低,且满足 VCP - VBAT < 6.8V\*后,电荷泵的保护会被触发,从而造成上桥驱动信号无法正常发出。

若上桥关闭时间一直大于 t\_blank+t\_filter,则电荷泵会一直保持正确的时间点接入 Vboot,则不会误触发以上电荷泵保护。所以可以如下操作:

- a) 设置较小的 t blank + t filter (推荐 t blank<=0.8us, t filter<=0.8us);

- b) 软件中保证上桥关闭时间不会小于上述时间。

## 2.4 下桥 Vds Monitor 功能应用限制与下桥 Vgs 走线

预驱的下桥驱动信号的返回路径为从 G 极到下桥的 S,再经过采样电阻,然后从芯片的 GND 返回。所以在下桥的 GS 走线时候下桥基极和 GND 就是一对走线。且下桥的 Vds monitor 参考点也是芯片的 GND,也就是下桥的 Vds monitor 监测的电压包含了下桥 Vds+V 采样电阻,所以会导致下桥的 Vds monitor 的检测偏差,在设置保护值的时候需要加以考虑。建议将 Vds monitor 作为二级保护,适当的放宽保护阈值。

在某些应用中如果一定要使用准确的 Vds monitor 功能,则可以将整个芯片和母线电容的 GND 参考点改为三相桥的下桥 S 极。这样将会得到精确的 Vds 电压。

#### 2.5 自举电容上电充电策略

SPD1188 上桥采用自举电容驱动的方式,在芯片上电之后,自举电容 CBOOT 是没电的,需要打开下桥利用 VDDG 通过自举二极管给 CBOOT 充电。CBOOT 电压不仅作为上桥 GS 的驱动电压,同时也是预驱上桥 Vgs 检测和控制电路的电源,当 CBBOT 电容电压在从 0V 充电到 VDDG-0.7V 的过程中,0V~3V 这段电压区间内,上桥驱动内部 Vgs 检测和控制电路可能会出现不正常工作。所以需要上电之后下桥打开给自举电容充电的时间必须足够长,让 CBOOT 电压很快的充电到 3V 以上。按照自举电容充电的电流可以计算出多长时间能够将自举电容充满,按照经验值对于 100nF 的自举电容器,下桥导通脉冲长度必须至少为 6us,并且对于较大的自举电容器值,脉冲长度必须与该数字成比例。

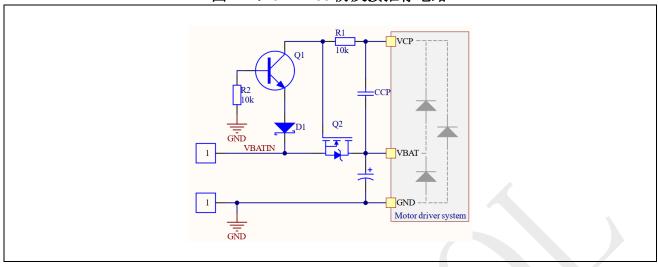

#### 2.6 防反接电路

防反接电路一般有如下方式实现:

- 1. 使用二极管电路实现, 劣势是二极管压降较大, 导通损耗比较大;

- 2. 使用正端的 PMOS 电路实现, 劣势是 PMOS 比较难找;

- 3. 使用负端的 NMOS 电路实现,劣势是对于一些敏感的采样电路,会因为 GND 的偏差,造成采样异常。

所以以下推荐一种使用 NMOS 的正端防反接电路,其中用到了 SPD1188 的 VCP 信号。

当电源正常接线时候,NPN 三极管 Q1 无 be 驱动电流,处于截止状态,D1 肖特基二极管用于阻断 Q1 可能出现的 eb 电流。NMOS Q2 寄生二极管保证电路的初始导通,VBATIN 将会施加到芯片 VBAT,当 Predriver 使能之后,VCP=VBAT+VDDG,此时 NMOS Q2 GS 电压等于 VDDG,Q2 完全导通,电路正常工作。

当电源反接时,芯片的 VCP 和 VBAT 由于电机驱动系统中寄生二极管影响,都近似等于反接的电源电压,NPN 三极管 Q1 正向导通,因为 Q1 导通,会把 Q2 的 Vgs 钳位到三极 Vce 管饱和压降+D1 二极管压降,约等于 1V 左右,这个电压保证了 Q2 处于关断状态,实现可靠的反接保护功能。

R1 和 R2 的选择要使系统在反接时, Q1 在处于饱和导通状态, 且处于正常的工作范围内。

图 2-4: SPD1188 防反接推荐电路

### 2.7 SIO CAN 通讯时钟精度要求

SPD1188 芯片内部集成了一个出厂校准到 32MHz 的 RC 振荡器时钟,内部 RC 时钟的特性如下图 2-5 所示,时钟的频率稳定度为±1%。

符号 参数 条件 最小 典型 最大 单位 供电电压 2.97 ٧  $V_{DDA}$ 3.3 3.63 RCO 时钟频率(室温条件下) T<sub>J</sub> = 25 °C 31.936 32.00 32.064 MHz FRCO RCO 时钟频率精度(RCO 时钟频率 T<sub>J</sub> = -40~125 °C % -1 1 **ACC**<sub>RCC</sub> 随温度的变化)

图 2-5: RCO 特性

在使用 SIO CAN 通讯网络时,根据 ISO11898-1(2015) CAN 通讯网络标准定义,对于 CAN 节点的时钟的稳定度有明确的要求,如果要使用 SIO CAN 网络通讯,尤其是多节点 CAN 网络通讯,那么内部的 RCO 时钟将不满足 CAN 网络对于时钟精度的要求,会导致 CAN 通讯出错。所以当需要使用到 CAN 通讯或者其他高速通讯网络的时候需要计算网络要求的时钟精度,当内部 RCO 时钟不能满足要求时,就需要增加外部石英晶振,才能满足 CAN 网络通讯的要求。