# SPD1188 DEMO 开发板使用手册

# 概述

SPD1188 是旋智科技针对 48V 应用推出的高压高集成度电机驱动 SOC,成功的应用在风机、自动升降桌等领域。

这份文档集中讨论了围绕 SPD1188 设计的 Demo 开发板各部分硬件电路的实现功能。

# 目录

| 1   | 开发    | 板介绍                        | 7  |

|-----|-------|----------------------------|----|

| 2   |       | 图功能描述及元器件选型参考              |    |

| 2.1 |       | <u> </u>                   |    |

|     | 2.1.1 | 启动模式配置                     | 9  |

| 2.2 | 电源及   | 及功率部分                      | 10 |

|     | 2.2.1 | 电源滤波及分压电路                  | 10 |

|     | 2.2.2 | 高/低压 BUCK 开关电源的外围降压电感和输出电路 | 10 |

|     | 2.2.3 | 电荷泵功能介绍及电容选取参考             |    |

|     | 2.2.4 | CBOOT 自举电容的选取参考            | 13 |

|     | 2.2.5 | 三相逆变电路设计参考                 |    |

|     | 2.2.6 | 采样电阻信号的两种处理方式              | 14 |

| 2.3 | 其它部   | 邻分                         | 15 |

|     | 2.3.1 | 时钟源选择电路                    |    |

|     | 2.3.2 | LED 显示电路                   |    |

|     | 2.3.3 | 芯片复位电路                     |    |

|     | 2.3.4 | SWD 烧录和 UART 接口            | 16 |

|     | 2.3.5 | 芯片工作模式切换电路                 | 17 |

# 图片列表

| 图 | 2-1:  | SPD1188.ENGR.20201105.V03 开发板原理图 | 8  |

|---|-------|----------------------------------|----|

|   |       | SPD1188.ENGR.20201105.V03 开发板实物  |    |

| 图 | 2-3:  | 电源滤波及分压电路                        | 10 |

|   |       | 高压 BUCK 输出电路                     |    |

| 冬 | 2-5:  | 低压 BUCK 输出电路                     | 11 |

| 冬 | 2-6:  | 电荷泵工作原理示意图                       | 12 |

| 冬 | 2-7:  | IRF640 关键参数                      | 13 |

|   |       | 三相逆变电路                           |    |

| 图 | 2-9:1 | .65V 偏置计算电路                      | 15 |

| 图 | 2-10: | 时钟源选择电路                          | 16 |

| 冬 | 2-12: | LED 显示电路                         | 16 |

|   |       | 芯片复位电路                           |    |

| 图 | 2-14: | SWD 烧录和 UART 接口                  | 17 |

| 冬 | 2-15: | 芯片工作模式切换电路                       | 17 |

# 表格列表

| 表 2-1 | :模式选择      | 9   |

|-------|------------|-----|

| -     | : 工作模式切换   |     |

|       | · 其他电容选值参考 | 4 2 |

# 版本历史

| 版本  | 日期         | 作者  | 状态  | 变更    |

|-----|------------|-----|-----|-------|

| C/0 | 2025-05-06 | 高天骥 | 已发布 | 首次发布。 |

# 术语或缩写

| 术语或缩写 | 描述                                           |           |

|-------|----------------------------------------------|-----------|

| MCU   | Microcontroller Unit,微控制器单元                  |           |

| UART  | Universal Asynchronous Receiver/Transmitter, | 通用异步收发传输器 |

|       |                                              |           |

|       |                                              |           |

|       |                                              |           |

# 1 开发板介绍

开发板名称: SPD1188.ENGR.20201105.V03

主芯片: SPD1188

应用场景: 针对 SPD1188 芯片全功能调试

- 开发板典型工作电压 8-50V, 最大工作电压 96V

- 额定输出电流 10A

- 板上含 32MHz 外置晶体,可灵活选择使用外部晶振或内部 RC 振荡电路作为时钟源

- 含三电阻电流采样信号 1.65V 偏置差分计算电路或使用芯片内部自带 3 路 MOTOR PGA 直接放大计算

- 集成3路增益可选差分运算放大器,14位ADC,温度传感器,过流保护比较器

- 集成直流母线电压和 VDDG 检测功能

- 集成双 BUCK (高压 BUCK, 低压 BUCK) 开关电源,配合外部降压电感及补偿网络可生成 VDDG 及 3.3V 电压为芯片供电

- 多数引脚具备 ECAP 功能,捕获输入电平

- 具备 UART、IIC、SPI 通信能力

- 预驱部分集成自举二极管,配合 Charge Pump 电容和旁路电容,可输出 100%占空比

- 支持深度睡眠模式(电流低至15uA)和引脚唤醒功能

# 2 原理图功能描述及元器件选型参考

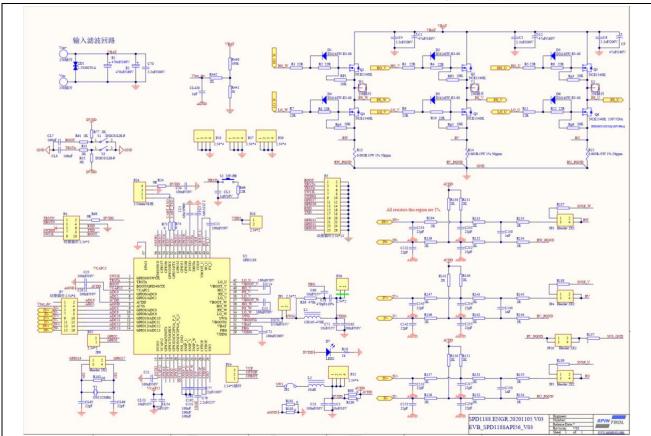

图 2-1: SPD1188.ENGR.20201105.V03 开发板原理图

图 2-2: SPD1188.ENGR.20201105.V03 开发板实物

## 2.1 硬件设置

## 2.1.1 启动模式配置

在开发过程中,用户可根据需要,通过跳线帽对开发板功能做出调整,以满足项目需求。

默认状态 跳线帽编码 功能描述 芯片模式选择参照表 2-2 GPIO40, TRSTn 均置高 S1, S3 高/低压 BUCK 开关电源电感 JP1, JP2 闭合 1.65V 偏置电路与 MOTOR JP3, JP4, JP5, JP10 **MOTOR PGA** PGA 选择 断开 JP6 时钟源选择

表 2-1: 模式选择

表 2-2: 工作模式切换

| 启动模式          | 白礼棋子      |        |

|---------------|-----------|--------|

| GPIO40 (BOOT) | RSTn 启动模式 |        |

| 0             | 0         | ISP 模式 |

| 0                                 | 1 | 工程测试模式,该模式下芯<br>片不能正常工作,任何时候<br>都不要选择该模式 |  |  |  |

|-----------------------------------|---|------------------------------------------|--|--|--|

| 工常启动模式,从 Flash 存器开始运行程序           |   |                                          |  |  |  |

| 特别说明: 当 TRSTn 为高电平时,芯片调试接口处于有效状态。 |   |                                          |  |  |  |

### 2.2 电源及功率部分

输入电源经过滤波电路作为板上的主电源,可通过芯片内部集成的 LDO 和双 BUCK 模块生成所需工作电压。对采样电阻的信号处理,存在两种方式,其一经过 1.65V 偏置计算电路再给到芯片引脚用于内部的 PGA 放大;其二可直接使用 MOTOR PGA 模块进行处理再做过流保护判断,也可通过 ADC 采样解析为各相电流值。为满足各相高占空比输出的需要,内部的自举二极管配合芯片外围器件构成电荷泵,可实现稳定的 100% 占空比输出。

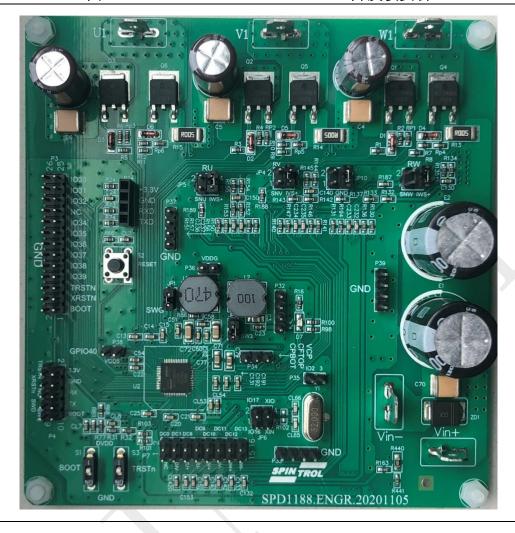

#### 2.2.1 电源滤波及分压电路

虽然芯片内部的高压模块具备 VBAT 检测功能,板上依然增设 VBAT 分压电路给到芯片引脚用以做精度比较。

图 2-3: 电源滤波及分压电路

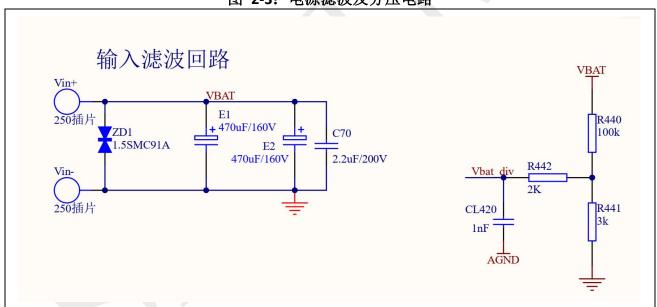

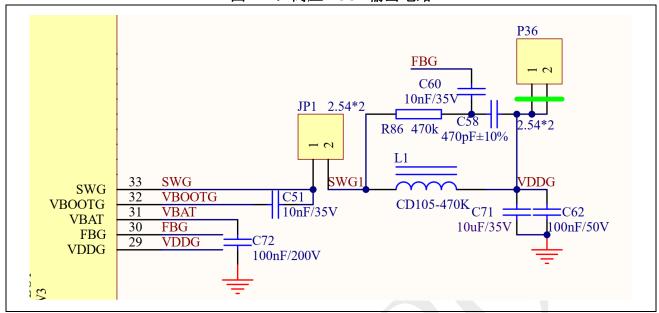

# 2.2.2 高/低压 BUCK 开关电源的外围降压电感和输出电路

SPD1188 内部集成 2 路 BUCK 开关电源, 其中高压 BUCK 用于生成 VDDG, 低压 BUCK 用于生成 3.3V 给芯片供电。

图 2-4: 高压 BUCK 输出电路

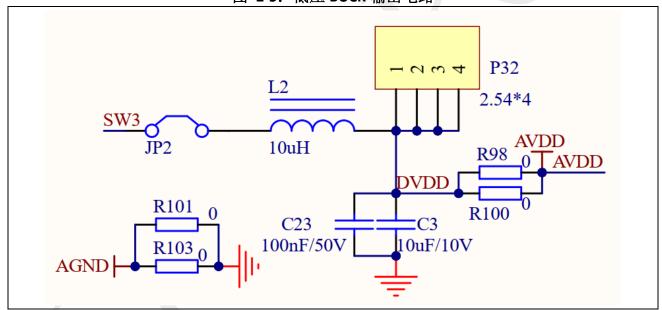

图 2-5: 低压 BUCK 输出电路

降压电感的选取: BUCK 可工作在 PFM 或 PWM 模式下,在实际应用中可强制锁定在 PWM 模式,电感大小影响着输出电压纹波的质量。通过理论分析,使用 PWM 模式的输出纹波更小,并且电感值越大,则纹波越小,但电感过大,会降低整个 Buck 控制的动态响应性能, 在经过系统设计优化后,建议选取的电感值为:

低压电感: L = 10uF ± 20%

高压电感: L = 47uF ± 20%

需注意的是低压 BUCK 电感的饱和电流需大于 500mA,因为 BUCK 的限流为该值,因此要求在极端情况下,电路也能稳定工作。而高压 BUCK 电感限流值为 300mA,是为防止对 VDDG 电源轨施加过多负载,且需额外增加补偿网络。

输出电容的选取:输出电容越大,纹波越小,综合稳定性考虑,建议:

低压电容:  $10uF \le C \le 15uF$

#### 高压电容: 22uF ≤ C ≤ 47uF

### 2.2.3 电荷泵功能介绍及电容选取参考

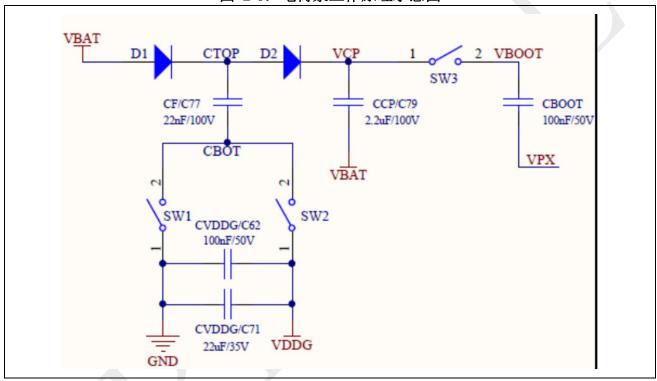

VDDG 电容、CF 电容和 VCP 电容在 Charge Pump 中会被交替使用。

电荷泵的工作主要分为两个阶段,其中内部 SW1 和 SW2 交替工作的开关频率约为 625KHz:

- 1) CF 电容下端 CBOT 连接到 GND, 此时 VBAT 如果高于 CTOP, 则 VBAT 向 CF 电容充电;

- 2) CF 电容下端 CBOT 连接到 VDDG, 此时 CTOP 电压如果高于 VCP 电压,则 CF 电容向 VCP 电容 CCP 充电。

图 2-6: 电荷泵工作原理示意图

当上桥持续打开后,VCP 开关会打开,此时如果 VCP 电压高于 Cboot 电压,则 CCP 电容向 Cboot 电容充电,可使上桥臂开关管持续导通。

基于上述过程在选取相关电容时应分别考虑如下:

1) CF 电容在上桥臂续流情况下需要完全供给 3 个上桥 Cboot 电容的电量, 所以在既定的 625kHz 的动作频率下, CF 电容至少要保证 Cboot 电压的稳定。设计时候保证 CFeffective (CFeffective ~625k\*CF) 大于 100 倍 3xCboot 就可以, 至少不低于 22nf 即可满足几乎所有应用需求。

$$CF \ge 22nF$$

2) CF 电容在向 VCP 充电时候,会从 VDDG 中抽取一部分电能,为了避免 VDDG 上的电压 出现突变,推荐 VDDG 电容为 22uf+100nf。

$$C_{VDDG} \ge 10 * CF$$

一般来说,该电容值越大 VDDG 会越稳定。另外 CF 电容上电压的变化也不希望引起 VCP 电容的剧烈突变,所以 CCP 电容也应尽可能多大于 CF 电容值,一般建议 CCP 电容选值为 2.2uf。

## 2.2.4 CBOOT 自举电容的选取参考

芯片内部集成电压型预驱模块,需在外围挂载自举电容 CBOOT 来为上管供电。虽然有电荷泵为外部 CBOOT 供电,但由于消隐和滤波时间的存在(最长约为 3.2us,可编程设置),在这期间上桥驱动有约 800uA 的漏电流还是会造成 CBOOT 电容电压的明显下降,甚至会影响到上管的开通。在经过这段时间后,电荷泵才会为 CBOOT 持续供电,维持稳定。其中电荷泵默认打开(推荐),但用户也可以根据实际需求来选择关闭。对于这两种情况下的 CBOOT 选取,有如下 2 种参考方法:

1) 通过参考公式进行计算:

$$C_{BOOT} \ge (800uA * \Delta t) / \Delta V$$

2) 为了防止因为 CBOOT 的电容不足,造成最后 Mosfet 的栅极电压不足,需要选取一个较大的 CBOOT 值,根据 Demo 上的 Mosfet 参数(Ciss 参数),推荐 3 个 CBOOT 为 100nf。

$C_{BOOT} \ge 10 * Ciss$

图 2-7: IRF640 关键参数

| Dynamic                                                                           |                  |   |      |   |    |

|-----------------------------------------------------------------------------------|------------------|---|------|---|----|

| Input Capacitance<br>V <sub>GS</sub> =0V,V <sub>DS</sub> =25V,f=1.0MHz            | C <sub>iss</sub> | - | 1300 | - |    |

| Output Capacitance<br>V <sub>GS</sub> =0V,V <sub>DS</sub> =25V,f=1.0MHz           | C <sub>oss</sub> | - | 430  | - | pF |

| Reverse Transfer Capacitance<br>V <sub>GS</sub> =0V,V <sub>DS</sub> =25V,f=1.0MHz | C <sub>rss</sub> | - | 130  | - |    |

其它部分电路电容的选型值参见下表。

表 2-3: 其他电容选值参考

| 网络名称    | 作用               | 选取基本原则                                              |

|---------|------------------|-----------------------------------------------------|

|         |                  | CVBAT $>$ 1.2W* $\triangle$ T/(Unorm <sup>2</sup> - |

|         |                  | Ushutdown <sup>2</sup> ),Unorm 是正常                  |

| VBAT    | 主电源电容            | 工作电压,Ushutdown 是掉电                                  |

| VBAT    |                  | 保护电压,W为主电源功率,                                       |

|         |                  | Δ T 为掉电后维持的工作时                                      |

|         |                  | 间。                                                  |

| VDD5    | 5V 电容            | CDVDD≥2.2uF,推荐 2.2uF                                |

|         |                  | 连接 4.7uf+0.1uf 去耦电容,或                               |

| AVDD    | 模拟 3.3V 电容       | 者至少要保证 2.2uF+0.1uf的                                 |

|         |                  | 配置                                                  |

|         |                  | 每个引脚上连接 2.2uf+0.1uf                                 |

|         | 数字 3.3V 电容       | 去耦电容;或者至少要保证每                                       |

| DVDD    |                  | 个引脚连接 0.1uf 去耦电容,                                   |

|         |                  | 且 DVDD 上的总电容和需要                                     |

|         |                  | 大于 <b>2.2</b> uf                                    |

| VCAP12  | <br>  系统 1.2V 电容 | 1.Pin4 的 VCAP12 引脚建议配                               |

| VCAF 12 | 水丸 1.2 V 电台      | 置一颗 0.1uf 的去耦电容;                                    |

| 2.Pin16 的 VCAP12 引脚建议<br>配置 2.2uf+0.1uf 的去耦电容, |

|------------------------------------------------|

| 或者至少要保证 2.2uf+0.1uf                            |

| 的配置                                            |

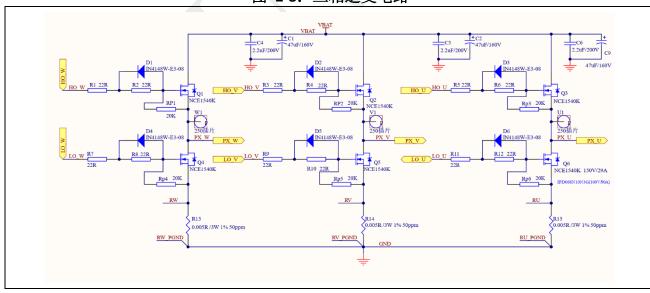

### 2.2.5 三相逆变电路设计参考

三相逆变电路是通过控制 3 路 6 个 MOS 管的导通或关断来驱动 PMSM 或 BLDC,是功率模块中最为核心的部分,Demo 上按照三电阻方案来设计采样电路。

1) 驱动电阻 R 的选择:考虑到布线导致的寄生电感 L 以及 MOS 自身 Cgs 的影响,MOS 驱动电路可等效成一个 RLC 串联电路,为一个二阶传函,而 MOS 管的栅源极电压一般都不希望出现上下震荡波形,故希望系统工作在临界阻尼和过阻尼状态,这就要求根分布在左半实轴上,故需使:

$$R \ge 2 * \frac{\sqrt{LC_{gs}}}{C_{gs}}$$

式中 L 为 PCB 上的走线电感,取 L=Length+10nH,其中 Length 单位为 mm。Cgs 即为栅源极电容,可参照 MOS 数据手册即可。依据上述理论,板上的驱动电阻推荐值为 2个 22ohm 电阻串联。

- 2) 由于 MOS 输入阻抗较高,为避免意外干扰导致的 MOS 管误导通,需在栅源极之间并 联电阻,以降低其输入阻抗,经验值选为 RP1=20K 即可。

- 3) 一般情况下,MOS 的关断时间大于导通时间,故为增大 Cgs 的泄放电流,提高 MOS 的关闭速度,在驱动电阻两端并联二极管即可。

图 2-8: 三相逆变电路

## 2.2.6 采样电阻信号的两种处理方式

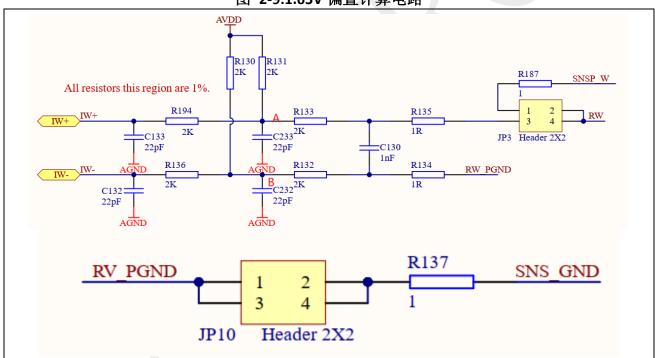

#### 1) 1.65V 偏置电路

由于采样电阻在电机运行时会出现负值信号,通过加入 1.65V 偏置才能确保给到芯片的信号为正值后再经过内部 PGA 模块放大处理,例举其中一路说明。将 JP3, JP4, JP5 三组跳线帽连接 3 和 4 引脚,RW 与 RW PGND 之间电压为 W 相采样电阻两端电压,经过 R135、 R134 和

C130 组成的滤波电路后进入偏置计算电路,然后将 AB 两点分别经过后级 RC 滤波电路后送入芯片引脚。

$$U_A = U_{RW} + \frac{3.3 - U_{RW}}{2} = 1.65 + U_{RW}/2$$

$$U_B = U_{RW\_PGND} + \frac{3.3 - U_{RW\_PGND}}{2} = 1.65 + \frac{U_{RW\_PGND}}{2}$$

$$U_A - U_B = (U_{RW} - U_{RWPGND})/2$$

由上式可知,该电路的输出端电压为输入端的一半,故芯片内部运放的实际放大倍数为 PGA/2。

#### 2) 内部 MOTOR PGA 直接放大

SPD1188 内部集成 3 路 MOTOR PGA 模块,其采样电阻两端信号不需计算偏置可直接送进芯片相应引脚进行检测。

将 JP3, JP4, JP5 三组跳线帽连接 1 和 2 引脚,同时将 JP10 跳线帽连接 1 和 2 或 3 和 4,将三相采样电阻负极与 SNS\_GND 相连即可。

图 2-9:1.65V 偏置计算电路

# 2.3 其它部分

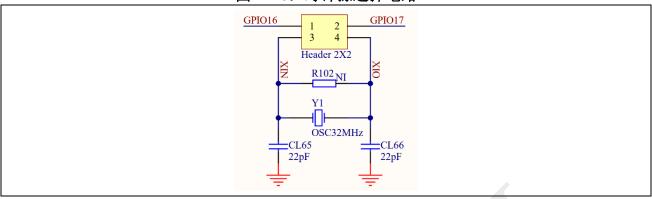

#### 2.3.1 时钟源选择电路

用户可通过 JP6 跳线帽短接 1,3 及 2,4 来启用外部晶振作为时钟源。

图 2-10: 时钟源选择电路

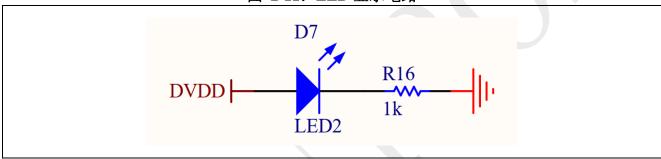

## 2.3.2 LED 显示电路

用户可通过 LED 灯能否被点亮来判断 DVDD 是否生成。

图 2-11: LED 显示电路

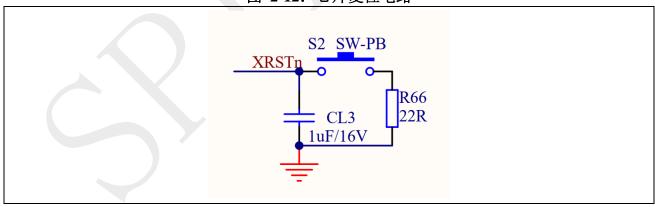

## 2.3.3 芯片复位电路

用于芯片复位和睡眠状态下的唤醒功能。

图 2-12: 芯片复位电路

### 2.3.4 SWD 烧录和 UART 接口

使用 SWD 协议烧录程序时,与仿真器的接线仅需 IO38: SWD、IO39: SWCK 以及 GND; USB 转串口分别连至 RX(GPIO35)、TX(GPIO34)以及 GND 即可,用于后期电机软件的调试。

0R R68 P4 **TRSTN DVDD** 1 2 **XRSTN** 3 4 **RXD** 5 6 SWDIO TXD 7 8 **SWCK** BOOT 9 10 双排插针2.54\*5

图 2-13: SWD 烧录和 UART 接口

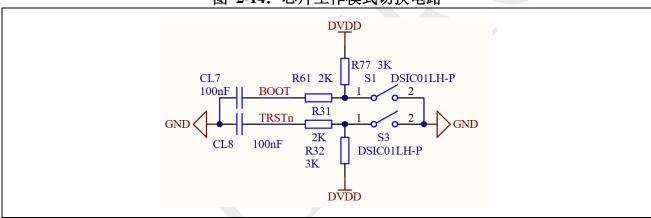

## 2.3.5 芯片工作模式切换电路

用户可根据表 2-2 对芯片工作模式做出选择。如使用 SWD 协议烧录程序,则需将两者全部置高;如使用 UART 接口烧录程序,则需两者全部置低,烧录后再将 BOOT 置高,程序即可从 flash 开始执行。

图 2-14: 芯片工作模式切换电路